# Lab Record On: VLSI Design

Tezpur University 2009-11

Submitted by:-

Sujit Kumar Nayak Roll no. – ELD09006 M.Tech ELDT, 2<sup>nd</sup> Sem

# **CONTENT**

- 1. Experiment-1: 4:1 MUX using Logic Gates.

- 2. Experiment-2: 16:1 MUX using Logic Gates.

- 3. Experiment-3: Nibble MUX using Logic Gates.

- 4. Experiment-4: Word MUX using Logic Gates.

- 5. Experiment-5: 4bit Up/Down Counter using Logic Gates.

- 6. Experiment-6: 9 bit Parity Generator using Logic Gates.

- 7. Experiment-7: Serial-In Parallel-Out Register using Logic Gates.

- 8. Experiment-8: Parallel- In Parallel-Out Register using Logic Gates.

- 9. Experiment-9: **3x3 ROM**.

- 10. Experiment-10: **3x2 RAM.**

## Experiment No -1: 4:1 Multiplexer using Logic Gates

#### **Theory:**

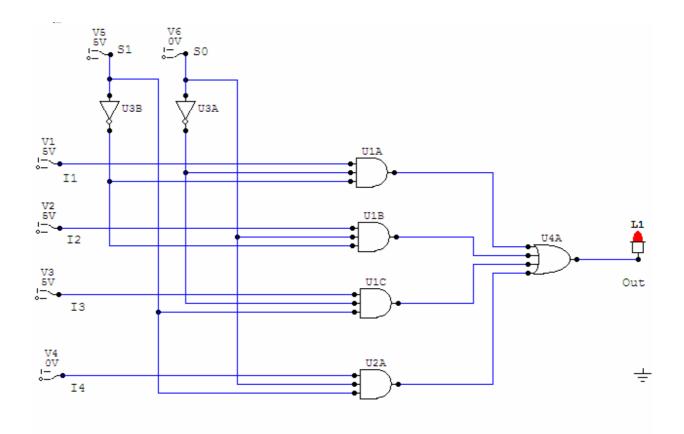

A multiplexer is a device having many inputs and one output. By applying control signals, any one of the inputs can be steered to the output. It can be an analog device or a digital device. Thus it is basically a single pole N throw selector switch. A 4:1 MUX is shown in the figure below. It has 4 inputs and 2 data select lines. A 2 bit binary code on the data select inputs allows the corresponding data to appear at output. If the number of inputs is 'N', then the required number of select lines is 'm' such that  $N=2^{m}$ .

Fig: 4:1 MUX

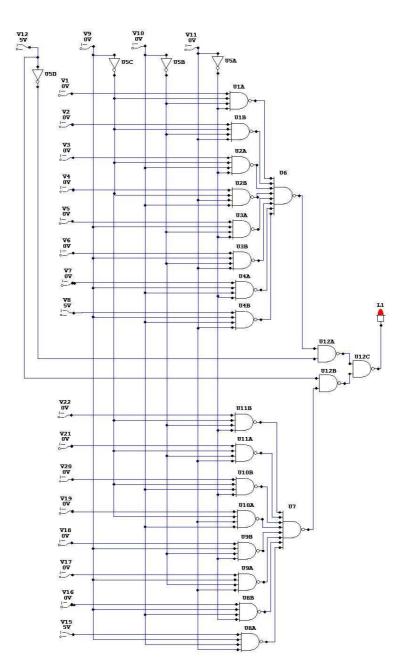

# Experiment No -2: 16:1 Multiplexer using Logic Gates

#### **Theory:**

A 16:1 MUX is shown in the figure below. It has 16 inputs and 4 data select lines. A 4 bit binary code on the data select inputs allows the corresponding data to appear at output.

#### Experiment-3: Nibble MUX using Logic Gates

A nibble contains 4 bits. So, there are sixteen (24) possible values, so a nibble corresponds to a single hexadecimal digit A full byte (octet) is represented by two hexadecimal digits; therefore, it is common to display a byte of information as two nibbles. An 8-bit byte is split in half and each nibble is used to store one digit. The last nibble of the variable is reserved for the sign. Thus a variable which can store up to nine digits would be "packed" into 5 bytes.

# Experiment-4: Word MUX using Logic Gates

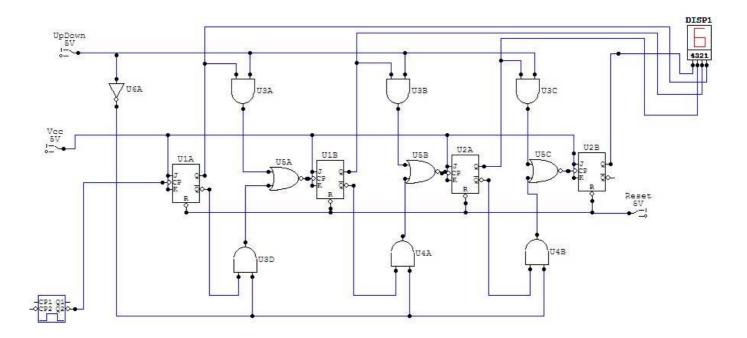

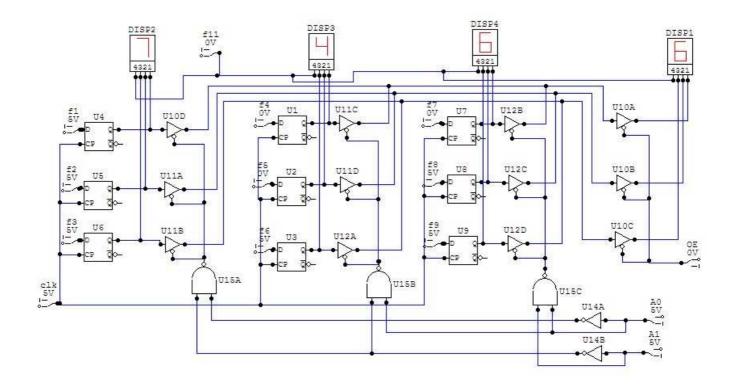

#### Experiment-5: 4bit Up/Down Counter using Logic Gates

#### **Theory:**

A 4 bit counter which counts from 0000 upwards is called up counter. A up counter counts from 0000 upwards. On the other hand, a down counter counts in the reverse direction. A 4 bit down counter counts from 1111 downwards to 0000. Fig 3 shows 4 bit up down counter.

Here a 4-bit counter that can count up, count down, or remain at the present value. The counter has four inputs RST, CLK, COUNT, and UPDN and one output VALUE. The UPDN input indicates which direction the counter should count. If COUNT = 1 and UPDN = 1, the counter counts up incrementing VALUE on every clock cycle (e.g. 0, 1, 2, ...). If COUNT = 1 and UPDN = 0, the counter counts down decrementing VALUE on every clock cycle (e.g. 5, 4, 3, ...).

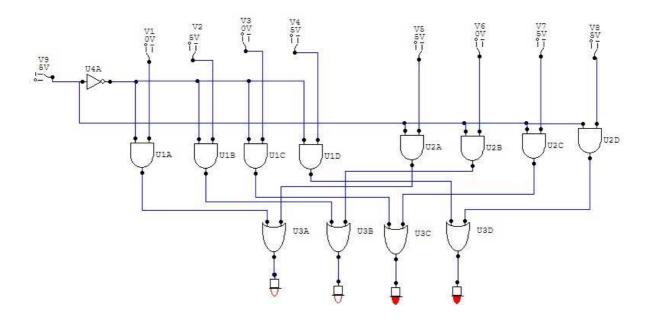

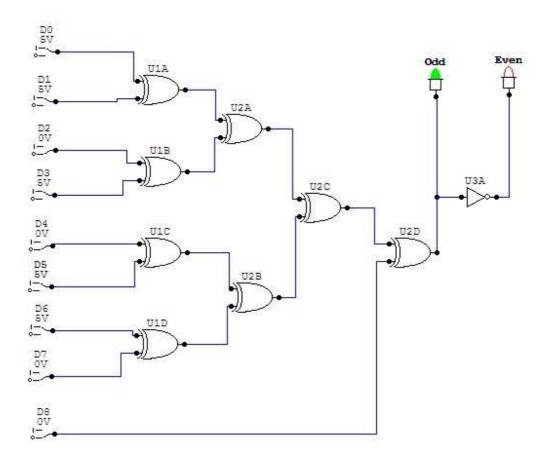

#### **Experiment-6**: **9 bit Parity Generator using Logic Gates**.

#### **Theory:**

Parity refers to the number of 1s in the binary word. When the number of 1s in the binary word is odd, it is said to have odd parity. When the number of words is even, it is said to have even parity. A parity bit is used for the purpose of detecting errors during transmission of binary information. The message including the parity bit is transmitted and then checked at the receiving end for errors. An error is detected if the checked parity does not correspond with the transmitted one.

Fig: 9 BIT PARITY GENERATOR

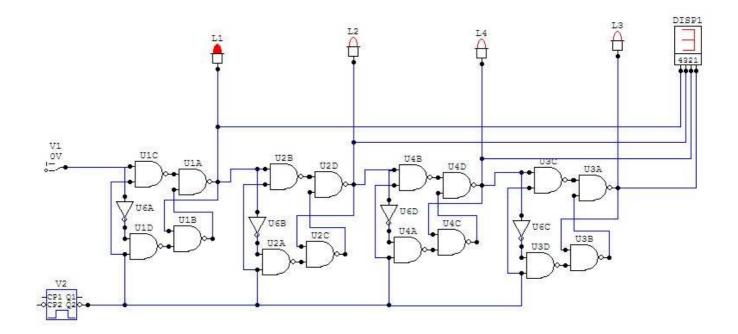

#### Experiment-7: Serial-In Parallel-Out Register using Logic Gates

#### **Theory:**

A flip flop can store 1-bit of digital information (1 or 0). It is also referred to as a 1-bit register. An array of flip flops is required store binary information, the number of flip flops required being equal to the number of bits in the binary word and is referred to as a register. Register find application in a variety of digital systems including microprocessor.

The data can be entered in serial or in parallel form. Data in serial form is also referred to as temporal code and in parallel form as special code

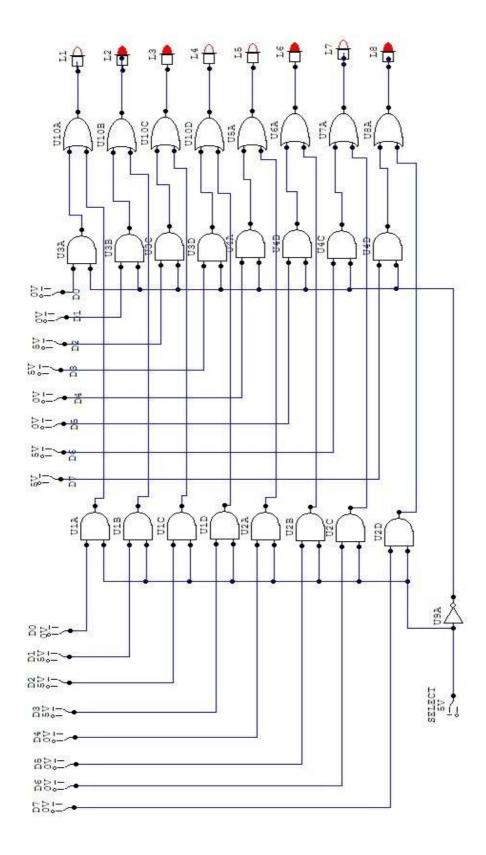

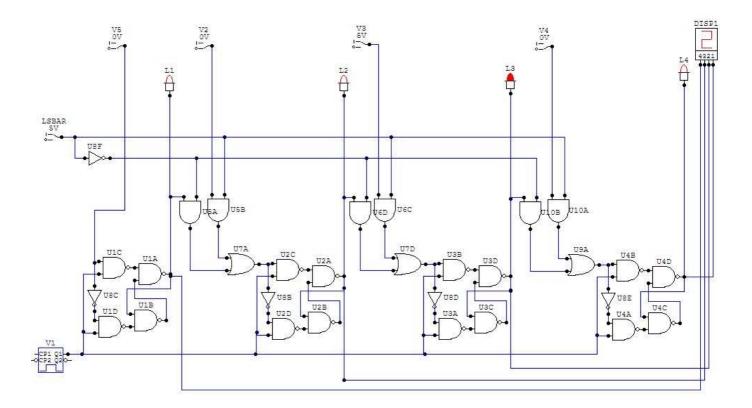

# Experiment-8: Parallel- In Parallel-Out Register using Logic Gates

#### **Theory:**

Registers are classified depending upon the way in which data are entered and retrieved. The data is loaded and read from the register in parallel, i.e. all bits are loaded simultaneously and read simultaneously.

Fig: CIRCUIT DIAGRAM OF PIPO REGISTER

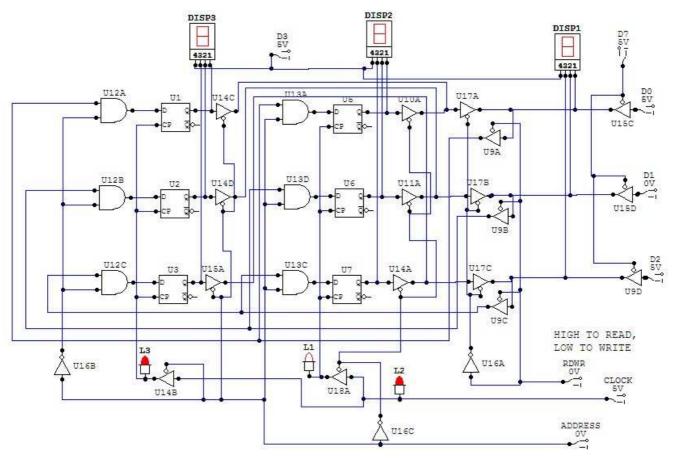

#### Experiment-9: **3x3 ROM**

# **Theory:**

. ROM is a non-volatile memory. ROM or Read Only Memory may be of permanent or semi permanent type. In permanent ROM, the data is permanently stored and cannot be changed. It can only be read from the memory. There cannot be a write operation because the specified data is programmed into the device by the manufacturer or the user. In semi permanent ROM also there is no write operation, but the data can be altered, to a limited extent, by special methods

FIG.8 : 3x3 ROM

## Experiment-10: 3x2 RAM

#### **Theory:**

RAM is an acronym for Random Access Memory. Both read and write operations are possible with this memory. RAM is a volatile memory and the data is lost if electric supply is switched off.

Since RAM is a volatile memory it can be used only for temporary storage of data. Thus it is suitable for calculations, buffer memories etc. RAM can be static or dynamic.